# Integration asynchroner Schaltungsansätze zur Verringerung der Verlustleistung in dynamischen Schaltungstechniken mit Einphasentakt

F. Grassert, D. Timmermann

## Übersicht

- Motivation

- Dynamische Schaltungstechniken

- Asynchrone Kopplung

- Ergebnisse

- Zusammenfassung

### **Motivation**

- Schnelle Schaltkreise

- Aufwendige Berechnungen (z.B. Kryptographie)

- → Dynamische Schaltungstechniken

- Niedrige Verlustleistung

- Drahtlose, batteriebetriebene Geräte

- → Asynchrone Logik

- Einfache, automatische Synthese

- Kurze Entwicklungszeiten

- → Einphasentakt

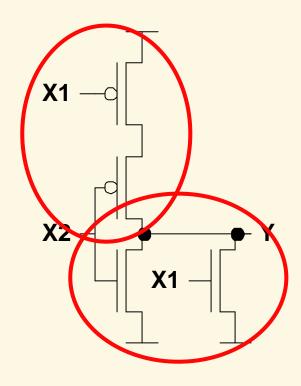

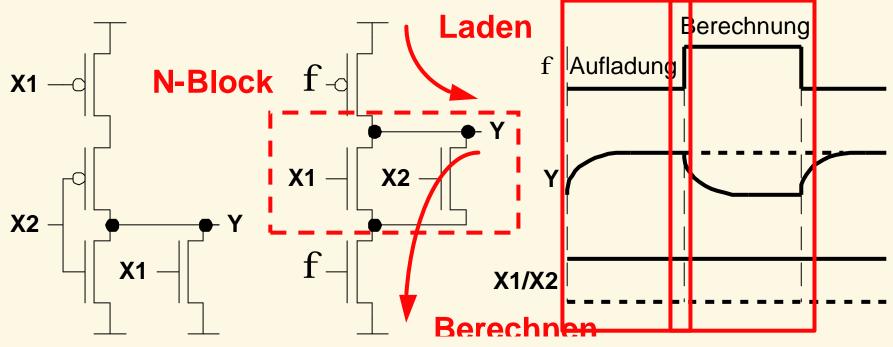

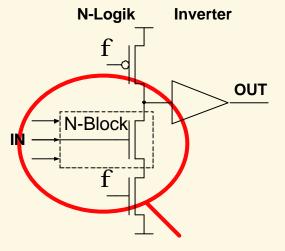

# Dynamische Schaltungstechnik

# Dynamische Schaltungstechnik

# Dynamische Schaltungstechnik

- Knoten wird geladen

- Entladung je nach Eingangszustand

- + schnell, da nur N-Transistoren

- Stromverbrauch auch bei konstanten Eingängen möglich

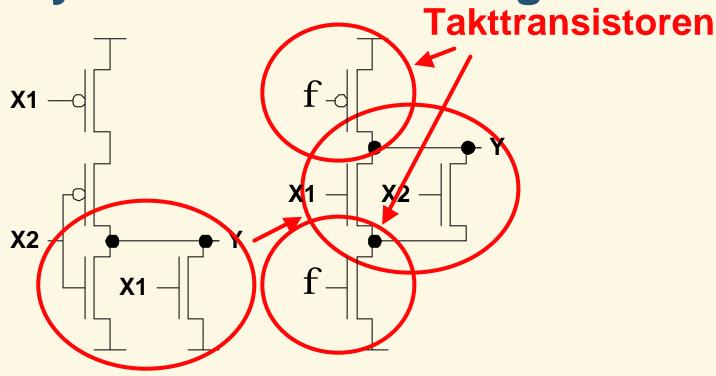

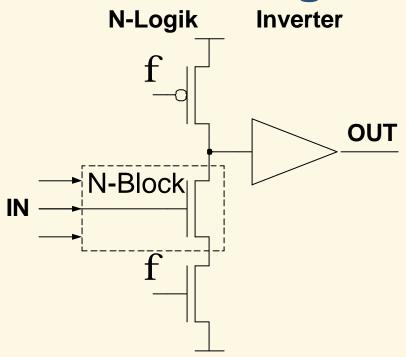

# **DOMINO Logik**

- Nur nichtinvertierende **Funktionen**

- 2-Phasentakt

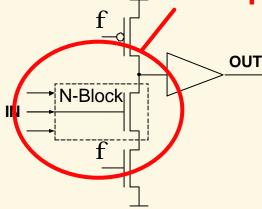

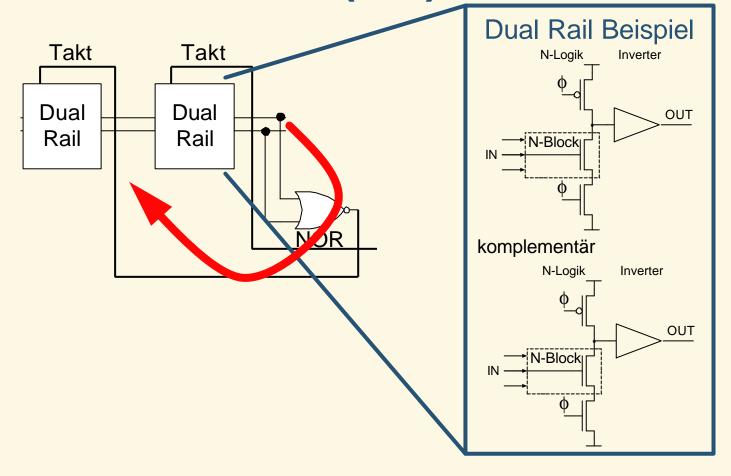

# **DOMINO Logik – Dual Rail**

- Ladephase: Ausgänge gleich

- Berechnungsphase: komplementäre Ausgänge

N-Logik In Keomplementäre Logikenf-timed Signale

# Ansätze zur Verlustleistungsreduktion

### Allgemein:

Verringerung der Kapazitäten, Reduzierung der Spannung usw.

### Dynamische Logik:

- → Verringerung der Taktbelastung

- im Takt bis zu 60% des gesamten Verbrauches

- → Einsatz asynchroner Ideen:

- z.B. global asynchron lokal synchron

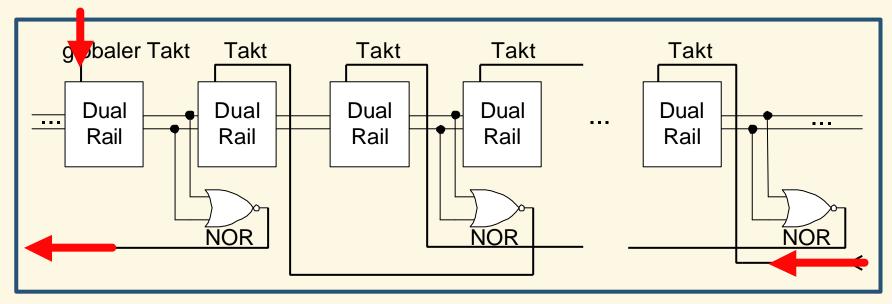

- ► Unser Ansatz: kürzeste Ketten asynchroner Logik

Asynchronous Chain (AC) – TSPC\*

\*Asynchronous Chain – True Single Phase Clock

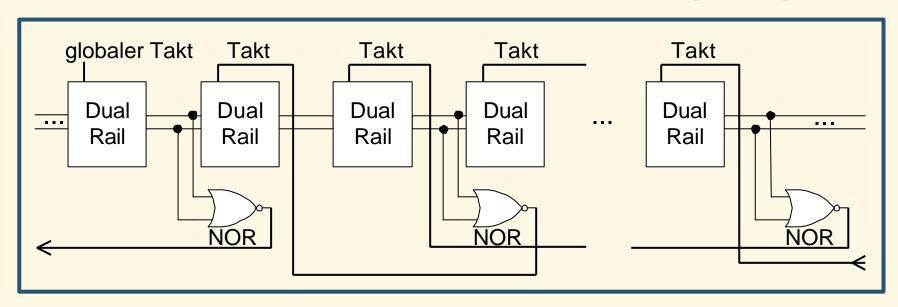

# Asynchronous Chain (AC) – TSPC

- Durchlauf startet mit Eintreffen des globalen Taktes

- Asynchrone Abarbeitung der Kette

- Letzte Stufe wartet auf Self-timed Signale der folgenden Kette - Registerfunktion

# AC – TSPC – Funktionsbedingungen

- Globaler Takt > einzelne Zykluszeiten

- Globaler Takt = Berechnungszeit des kritischen Pfades (keine zusätzliche Verzögerung)

- Erzeugung der Self-timed-Signale unter Beachtung paralleler Ketten

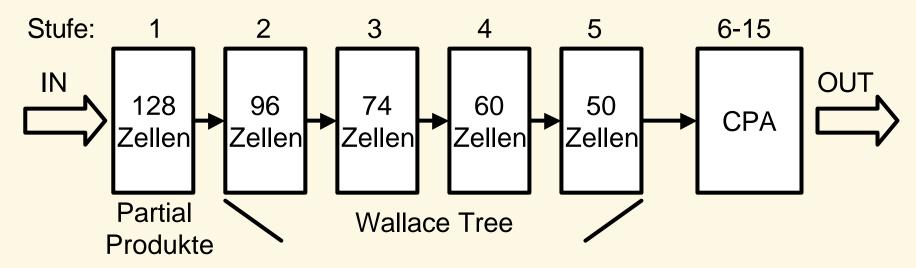

# Beispiel – Wallace Tree Multiplizierer

• 8x8 Bit Multiplizierer:

- Pipeline mit 15 Stufen 15 Takte für eine Multiplikation

- AC-TSPC: 5 Stufen pro Taktzyklus 3 Takte für Multiplikation

# **Ergebnisse**

Beispiel: Wallace-Tree Multiplizierer; Backannotation

|                     | Stat. CMOS | Stat. CMOS | AC-TSPC |

|---------------------|------------|------------|---------|

|                     | 15 Stufen  | 3 Stufe    | 3 Stufe |

| Verbrauch           | 1          | 8.0        | 8.0     |

| Latenzzeit          | 1          | 0.3        | 0.2     |

| Power-Delay-Produkt | 1          | 0.23       | 0.16    |

Relative Werte für 0.6µm/3.3V (AMS)

### Synthese:

- Kurze Ketten → einfaches Berechnungsschema für asynchrone Teile → extern synchrones Verhalten

- Automatische Synthese möglich, aber mehr Schritte

# Zusammenfassung

- Verringerter Verbrauch und Latenzzeit mit kurzen asynchronen Ketten in einem global synchronen Design

- Aber: Reduzierter Durchsatz

- Einfacherer Takt und robuster gegen Taktschwankungen

- Synthese:

- Aufspaltung des Designs in asynchrone Teile, Parameterprüfung

- Anordnung der synchronen Blöcke

- Verwendung verschiedenster Schaltungstechniken (aber Dual Rail)