Maritimes Symposium 2007, Rostock

Frank Sill, <u>Claas Cornelius</u>, Dirk Timmermann 09. Oktober 2007

## Ziel dieser Arbeit

Einführung eines Ansatzes zur Leckstromreduzierung

2. Vorstellung eines erweiterten

Zuweisungsalgorithmus für Ansätze auf

Gatterebene

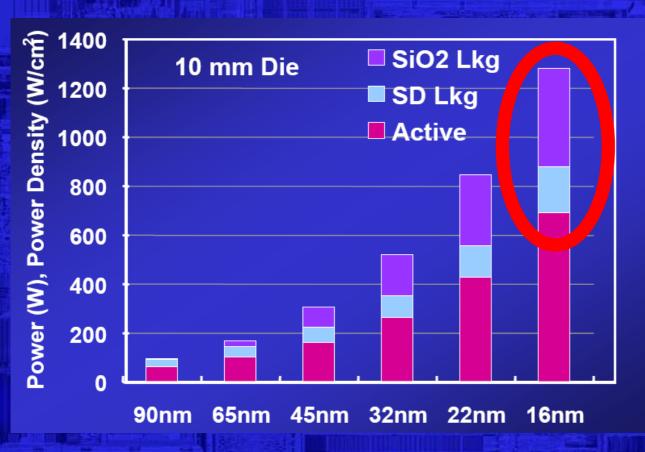

### Motivation

Bis zu 50 % wird (*ist !*) Leckstrom!

**SiO2 Lkg** - "Gate oxide" Leckstrom ( $I_{gate}$ )

**SD Lkg** – "Subthreshold" Leckstrom (*I<sub>sub</sub>*)

S. Borkar, '05

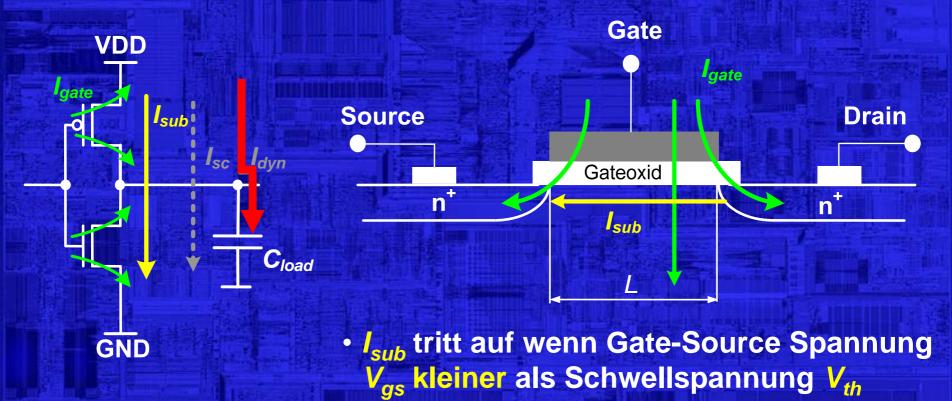

# Leistungsverbrauch in CMOS-Schaltungen

I<sub>gate</sub> basiert auf "Tunnelströmen" durch das Gateoxid

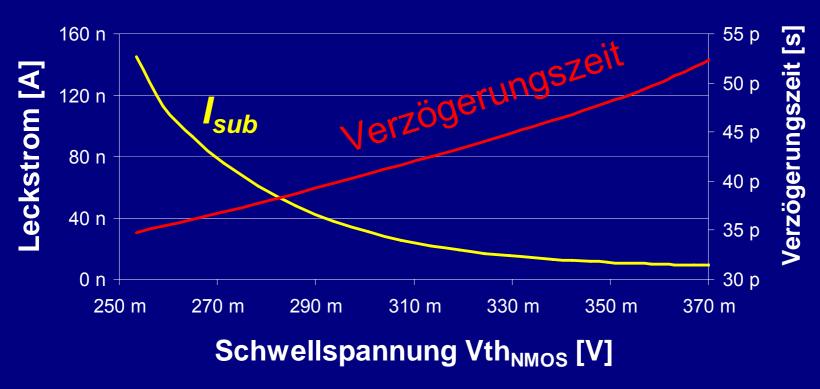

# V<sub>th</sub>, Verzögerungszeit und Leckstrom

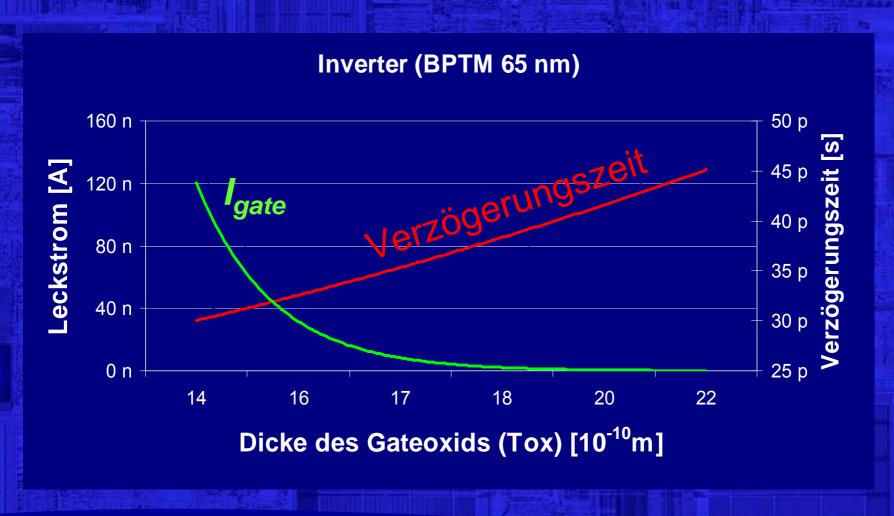

# T<sub>ox</sub>, Verzögerungszeit und Leckstrom

### Dual - $V_{th}/T_{ox}$ - Ansätze

Einsatz von zwei unterschiedlichen Transistortypen:

- "low-V<sub>th</sub>"- oder "low-T<sub>ox</sub>"-Transistoren

- Niedrige Schwellspannung oder dünne Oxidschicht

- Für zeitkritische Bereiche

- Führt zu hohem Leckstrom

- "high-V<sub>th</sub>" oder "high-T<sub>ox</sub>"-Transistoren

- Hohe Schwellspannung oder dicke Oxidschicht

- Für zeitunkritische Bereiche

- Führt zu niedrigem Leckstrom

### Dual - $V_{th}/T_{ox}$ - Ansätze

Einsatz von zwei unterschiedlichen Gattertypen:

- Gatter mit "low-V<sub>th</sub>"- oder "low-T<sub>ox</sub>"-Transistoren

- Niedrige Schwellspannung oder dünne Oxidschicht

- Für zeitkritische Bereiche

- Führt zu hohem Leckstrom

- Gatter mit "high-V<sub>th</sub>" oder "high-T<sub>ox</sub>"-Transistoren

- Hohe Schellspannung oder dicke Oxidschicht

- Für zeitunkritische Bereiche

- Führt zu niedrigem Leckstrom

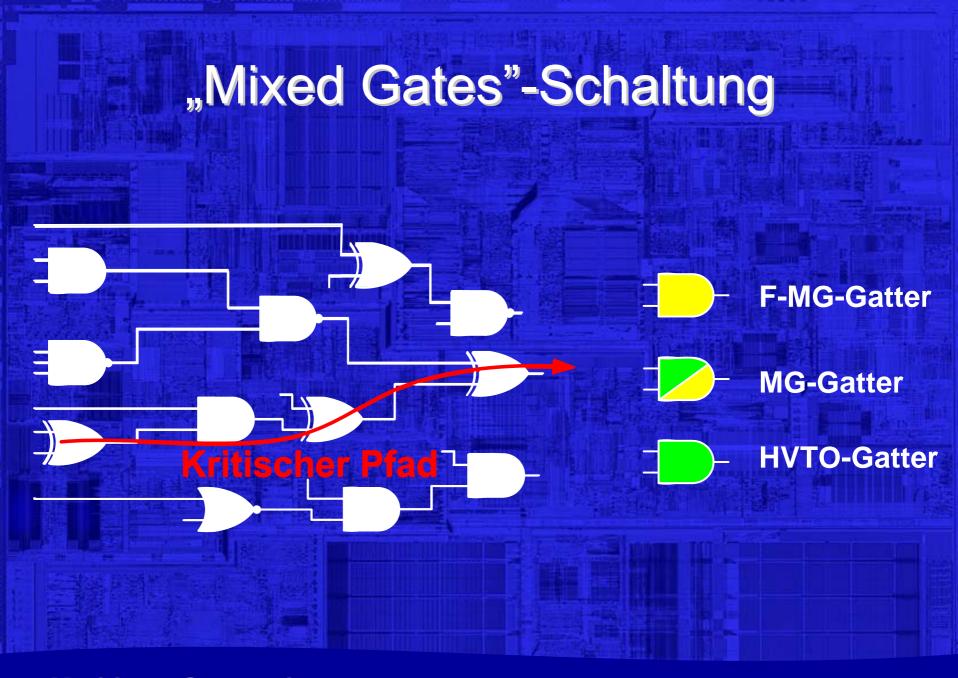

### Der "Mixed Gates" Ansatz

- Bisherige Ansätze:

- Ansatz auf Transistorebene

- Logische Gatter nur mit einem Transistortyp

- Transistoren unterscheiden sich nur in  $V_{th}$  oder  $T_{ox}$

- Zwei Gattertypen

- Mixed Gates:

- Gatter aus unterschiedlichen Transistortypen

- Transistoren unterscheiden sich in  $V_{th}$  und  $T_{ox}$

- Drei Gattertypen

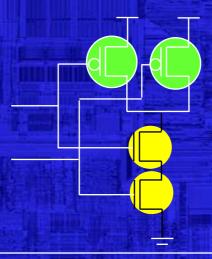

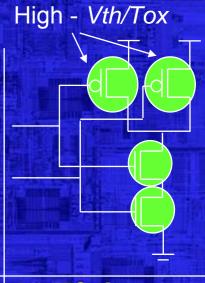

### "Dual Gates" - NAND2

Low - Vth/Tox

#### LVTO-Gatter

- MinimaleVerzögerungszeit

- Sehr großer Leckstrom

#### **HVTO-Gatter**

- MaximaleVerzögerungszeit

- Minimaler Leckstrom

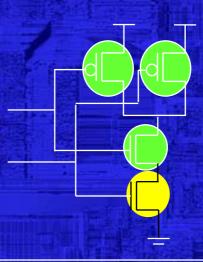

## "Mixed Gates" - NAND2

Low - Vth/Tox

#### LVTO-Gatter

- MinimaleVerzögerungszeit

- Sehr großer Leckstrom

#### F-MG-Gatter

- MinimaleVerzögerungszeit

- großer Leckstrom

#### **MG**-Gatter

- MittlereVerzögerungszeit

- MittlererLeckstrom

#### **HVTO-Gatter**

- MaximaleVerzögerungszeit

- MinimalerLeckstrom

### Zuweisung der Gattertypen

- Bestimmung Gattertypen über prioritätsbasierte Zuweisungsalgorithmen (PZA)

- PZA nutzen Bewertungsfaktoren zur Charakterisierung der Gattertypen und Gatter

- Zuweisung der Gattertypen anhand der Bewertungsfaktoren

- Bekannte Algorithmen:

- Kato [Kat00]: Keine Betrachtung der Gattertypen

- Engel [Eng06]: Betrachtung von Gattertypen

- Li [Li93] : Betrachtung von Gattertypen und teilweise maximal/minimal Werten innerhalb der Schaltung

### **Neuer Algorithmus**

- Verwendete Bewertungsfaktoren:

- t<sub>slack</sub> maximale Erhöhung der Gatterverzögerungszeit ohne Auswirkungen auf Schaltungs-Performance

- t<sub>d\_diff</sub> Änderung der Gatterverzögerungszeit durch die Zuweisung von neuem Gattertyp

- I<sub>leak\_diff</sub> Änderung des Gatterleckstroms durch die Zuweisung von neuem Gattertyp

- n<sub>p</sub> Anzahl der Pfade, in denen sich das Gatter befindet

- Alle Parameter relativiert zu minimalen und maximalen Werten innerhalb der Schaltung

### **Neuer Algorithmus**

- Hoher Gatterbewertungsfaktor ( = hohe Wahrscheinlichkeit für Zuweisung von "Low Leakage"-Gattertyp) wenn:

- Gatter in wenigen Pfaden  $(n_p \downarrow)$

- Hohe Leckstromdifferenz (I<sub>leak diff</sub> ↑)

- Geringe Verzögerungszeitdifferenz (t<sub>d diff</sub> ↓)

- Großer Slack (t<sub>slack</sub> ↑)

- Bewertungsfaktoren werden gewichtet

- Zusätzlich Anpassung aller Parameter anhand Verteilungsfunktion → reduziert Einfluss von Extremwerten

### **Neuer Algorithmus**

Wichtung der Parameter

Anpassung wg. Einfluss von Extremwerten

$$\mathcal{Y} = \kappa_{np} \left( 1 - \left[ n_{P\_r} + n_{P\_add} \right] \right) + \kappa_{lleak} \left[ I_{leak\_diff\_r} + I_{leak\_diff\_add} \right] \dots$$

$$\dots + \kappa_{td} \left( 1 - \left[ t_{d\_diff\_r} + t_{d\_diff\_add} \right] \right) + \kappa_{slack} \left( t_{slack\_r} + t_{slack\_add} \right)$$

$$\boldsymbol{X}_{\_r} = \frac{\boldsymbol{X}_{max} - \boldsymbol{X}}{\boldsymbol{X}_{max} - \boldsymbol{X}_{min}}, \boldsymbol{X} \in n_P, \boldsymbol{I}_{leak\_diff}, \boldsymbol{t}_{d\_diff}, \boldsymbol{t}_{slack}$$

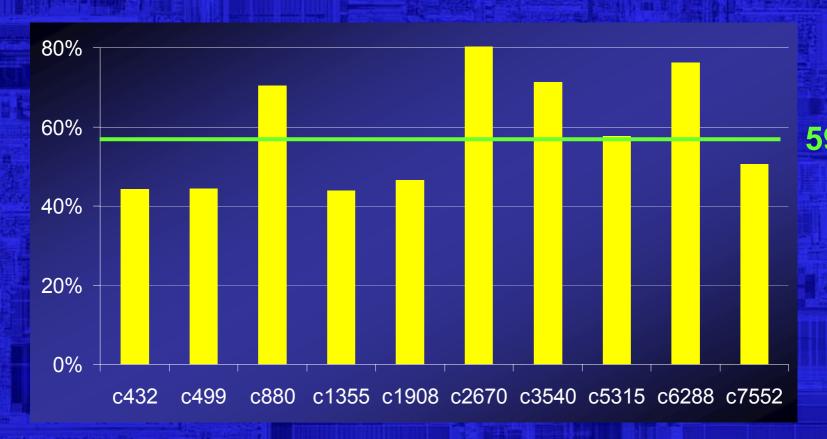

# Resultate: "Mixed Gates"

Leckstromreduzierung durch Anwendung des "Mixed Gates"-Ansatzes (bei konstanter Performance)

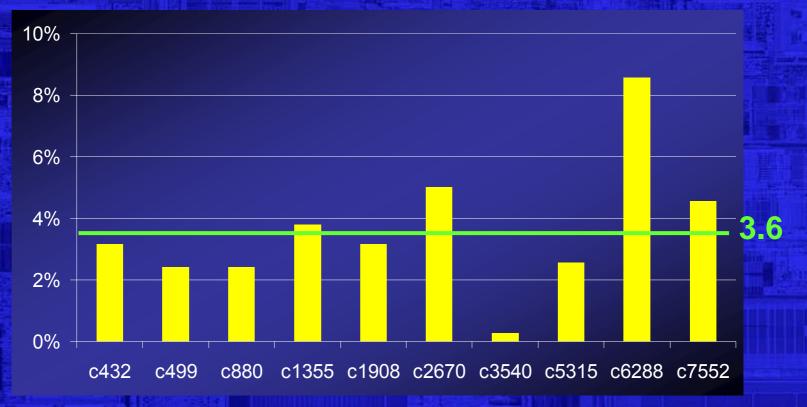

### Resultate: PZA-Vergleich (Leckstrom)

Zusätzliche Leckstromreduzierung durch den neuen Algorithmus gegenüber bekannten Algorithmen

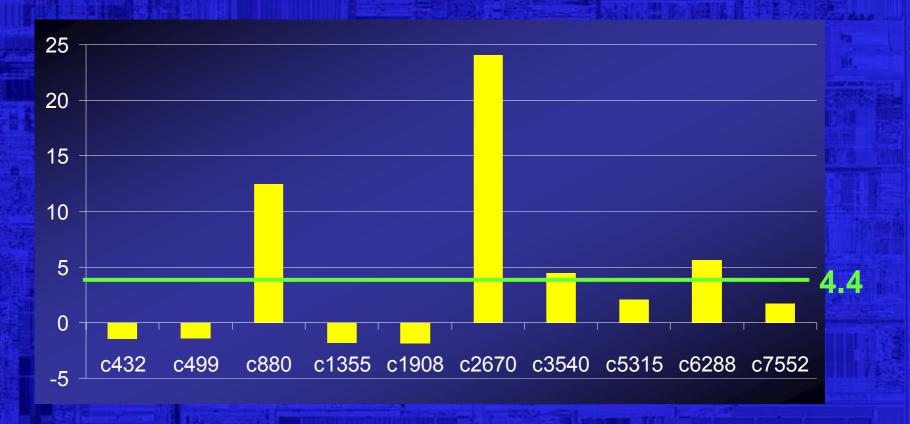

### Resultate: PZA-Vergleich (Aufwand)

Reduzierung des Rechenaufwands durch den neuen Algorithmus gegenüber bekannten Algorithmen

# Zusammenfassung

- Einfluss des Leckstroms auf Energieverbrauch steigt stetig an

- "Mixed Gates"-Ansatz verwendet unterschiedliche Transistorentypen innerhalb der Gatter

- Drei "Mixed Gates"-Gattertypen mit verschiedenen Verzögerungszeiten und Leckströmen

- Neuer Zuweisungsalgorithmus reduziert Einfluss von Extremwerten

- "Mixed Gates"-Ansatz reduziert Leckstrom um durchschnittlich 59 %

### Referenzen

- [Eng06] Engel, K.; Kalinowski, T.; Labahn, R.; Sill, F.; Timmermann, D. "Algorithms for Leakage Reduction with Dual Threshold Design Techniques", In *Proc. of Intern. Symposium on System-on-Chip* (SOC), pp. 111-114, Tampere, Finland, 2006.

- [Kat00] Kato, N. et al. "Random Modulation: Multi- Threshold-Voltage Design Methodology in Sub-2V Power Supply CMOS", In *IEICE Transactions on Electronics*, vol. E83-C, no. 11, pp. 1747-1754, November 2000.

- [Li93] Li, W. N.; Lim, A.; Agrawal A.; Sahni, S. "On the circuit implementation problem", In *Proceedings of ACM/IEEE Conference on Design Automation* (DAC), pp. 478-483, 1993.