### Advance VLSI Design (Module 24151) Phase 3

Hooma Amjad

#### **Aim of Phase 3 Task**

Final FPGA Design

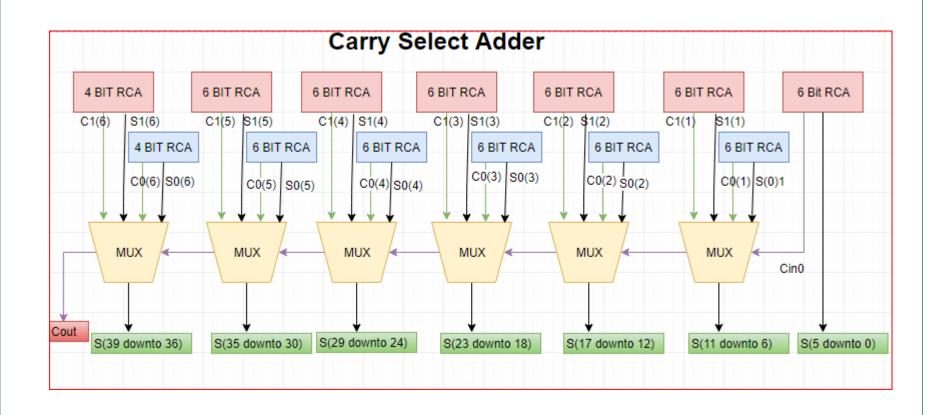

#### **Design and Architecture**

#### **Signed Wallace Tree Multiplier**

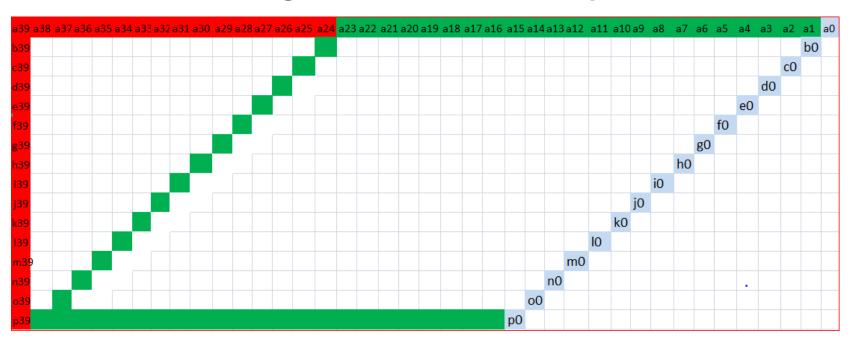

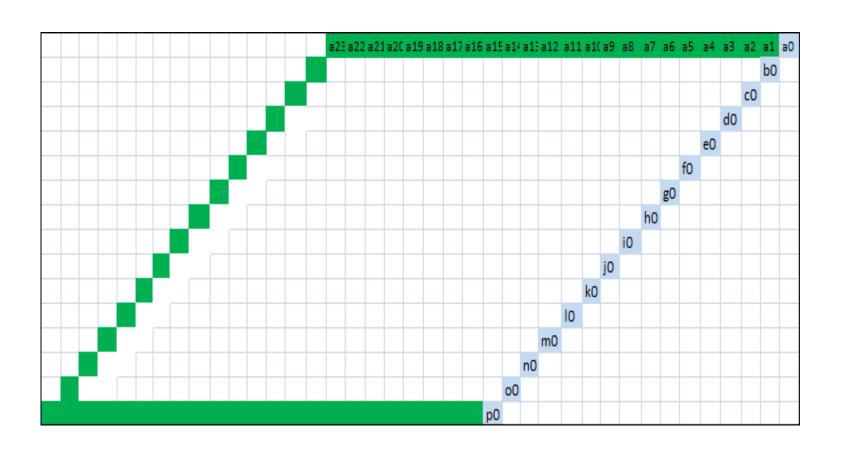

#### Improved Wallace Tree Multiplier

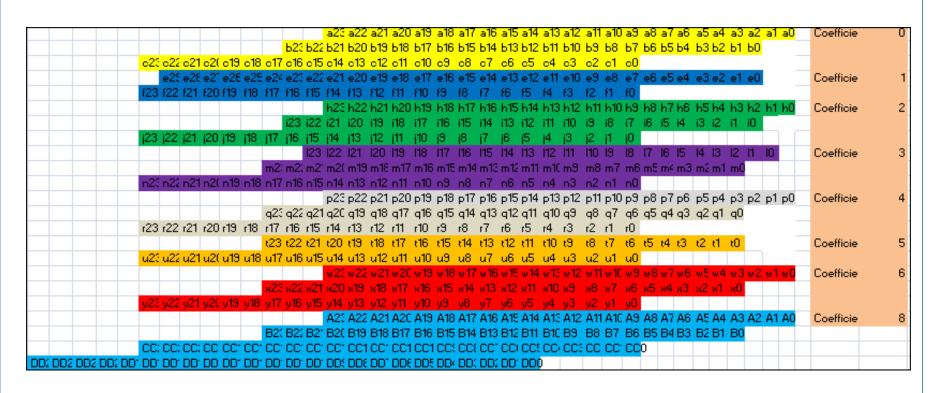

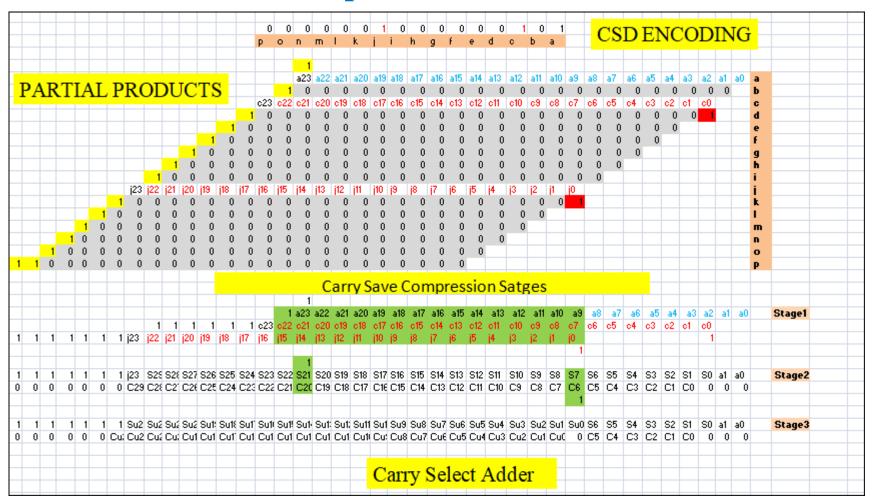

## **CSD Encoded Wallace Tree Multiplier Reduced Partial Products.**

#### **Multiplier Internal Structure**

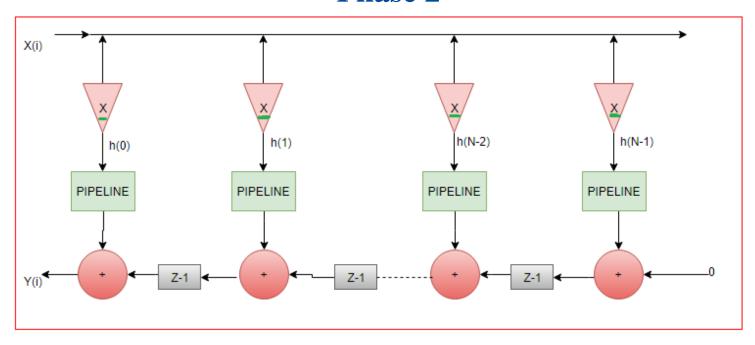

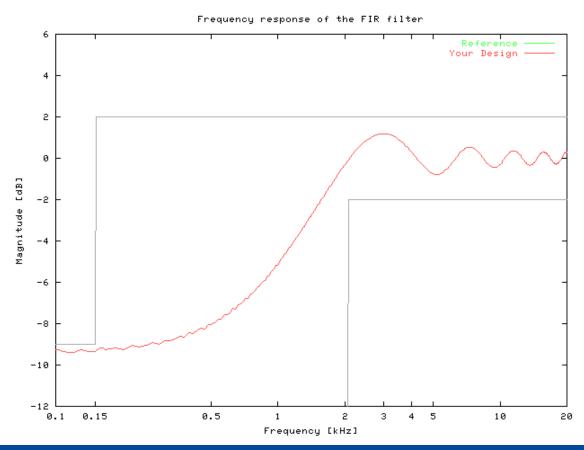

## Pipelined Direct form II Phase 2

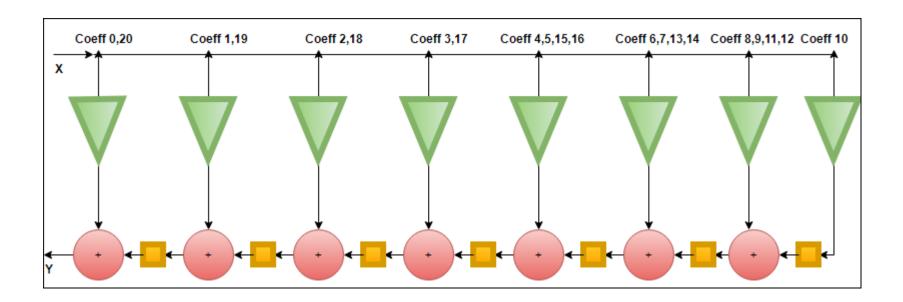

#### **Term Sharing**

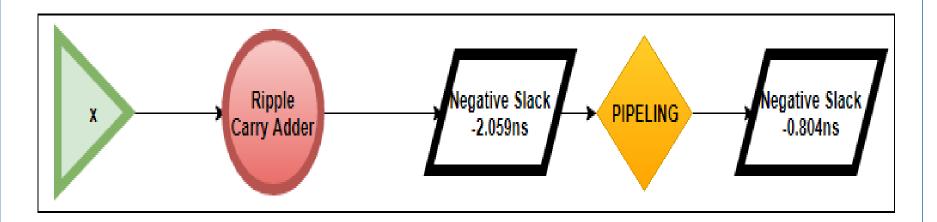

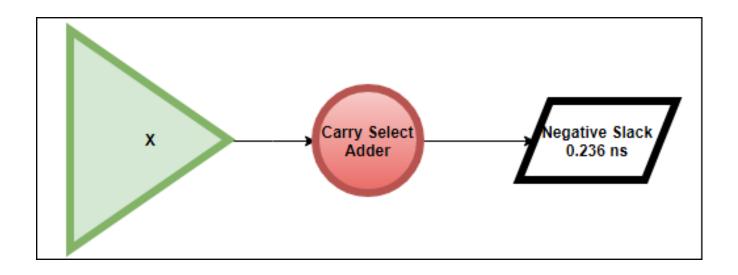

#### **Issues**

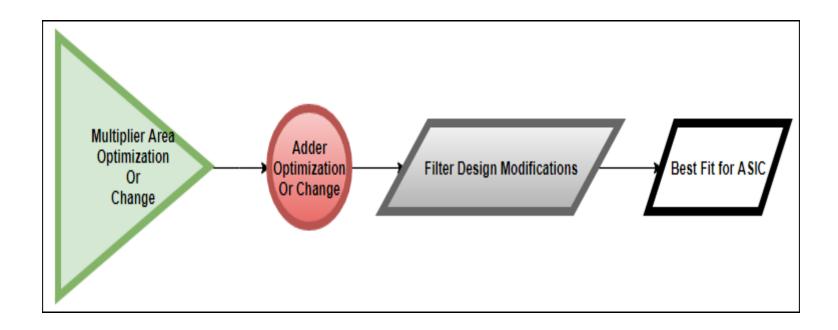

#### **Solution**

#### Design Values Comparison

| Phase 2           |                      |

|-------------------|----------------------|

| Frequency         | 100MHz               |

| Area              | LUT: 4134 / FF: 2148 |

| # Pipeline Satges | 2                    |

| Phase 3           |                    |

|-------------------|--------------------|

| Frequency         | 100MHz             |

| Area              | LUT: 2413 / FF:835 |

| # Pipeline Satges | 0                  |

#### Further Improvements

#### Result

Worst Negative Slack: 0.236 ns

# THANK YOU QUESTIONS?